Để xây dựng bộ đếm thập phân đồng bộ có Kđ = 10 phải dùng ít nhất 4 FF, khi đó sẽ còn thừa 6 trạng thái không dùng đến (vì 4 FF mã hoá được tối đa 24 = 16 trạng thái).

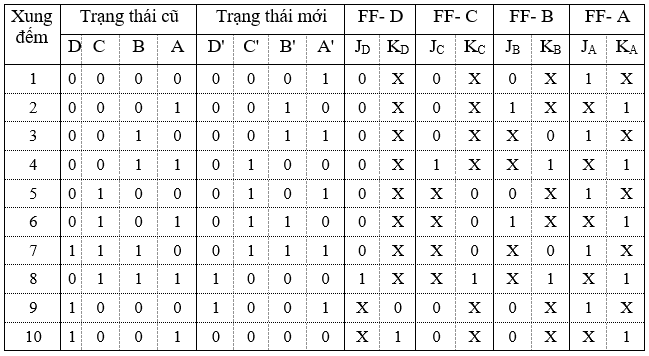

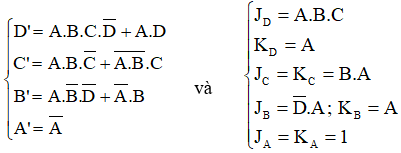

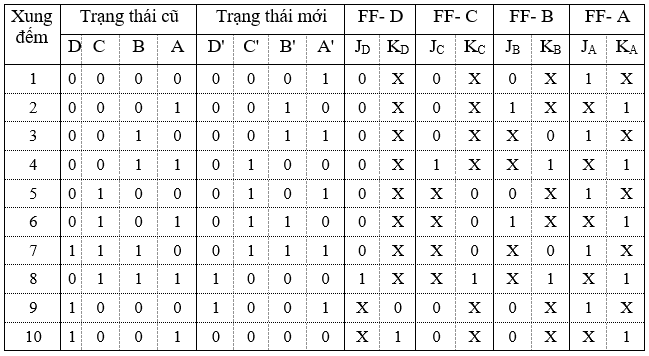

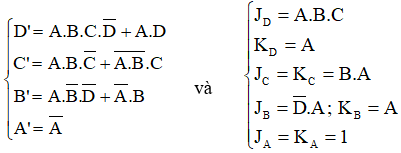

Bảng chuyển đổi trạng thái và đầu vào kích thích cho các FF loại JK của bộ đếm thập phân:

Từ bảng trạng thái ta thấy: FF-A chuyển trạng thái sau mỗi lần kích thích của xung đếm.

FF-B chỉ chuyển đổi trạng thái khi FFA từ 1 xuống 0 trừ trường hợp cuối cùng lúc FFD ở mức cao (D =1).

FF-Cchuyển đổi trạng thái khi FFB từ 1 xuống 0.

FF-D coi như chuyển trạng thái giống FFA tức là theo giá trị A từ 1 xuống 0 nhưng bị cấm trong suốt thời gian có xung nhịp từ 0 đến 7, cho tới khi B = C = 1 mới chuyển.

Bảng chuyển đổi trạng thái và đầu vào kích thích cho các FF loại JK của bộ đếm thập phân:

Từ bảng trạng thái ta thấy: FF-A chuyển trạng thái sau mỗi lần kích thích của xung đếm.

FF-B chỉ chuyển đổi trạng thái khi FFA từ 1 xuống 0 trừ trường hợp cuối cùng lúc FFD ở mức cao (D =1).

FF-Cchuyển đổi trạng thái khi FFB từ 1 xuống 0.

FF-D coi như chuyển trạng thái giống FFA tức là theo giá trị A từ 1 xuống 0 nhưng bị cấm trong suốt thời gian có xung nhịp từ 0 đến 7, cho tới khi B = C = 1 mới chuyển.

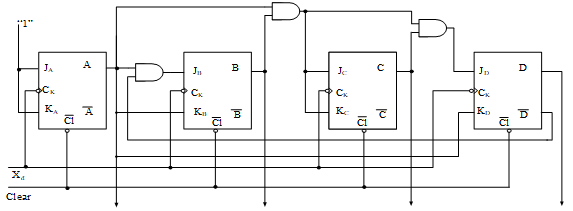

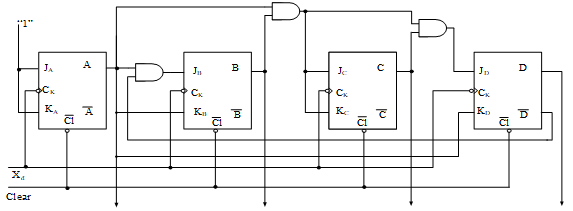

Sơ đồ logic mạch đếm thập phân đồng bộ dùng FF- JK.

Với mạch điện hình trên việc kích thích các FF thực hiện đồng bộ theo từng nhịp của xung đếm CK. Trừ FFA làm việc ở chế độ bập bênh thay đổi trạng thái theo mỗi nhịp, còn FFB, FFC và FFD chịu sự điều khiển cho phép hay không cho phép của các đầu vào điều khiển của chúng.

Bước 1: Khởi chạy sơ đồ mạch logic và sơ đồ mạch logic hiển thị LED. Quan sát tín hiệu đầu ra và giản đồ dạng sóng, đưa ra nhận xét?

Bước 2: Thay đổi tốc độ mô phỏng mạch và hiệu ứng tín hiệu của mạch bằng cách Click chuột vào các biểu tượng "Simulation Speed" và "Current Speed" tương ứng. Quan sát hiệu ứng trong mạch.

Bước 3: Thay đổi tần số của xung đồng hồ bằng cách Click đúp chuột vào biểu tượng "CLK". Quan sát tín hiệu ở đầu ra và giản đồ dạng sóng, So sánh với kết quả quan sát được ở bước thứ 1.

Bước 4: Tiến hành thực hành trên Test Board, Khởi chạy mạch lắp ráp. Quan sát tín hiệu ra, đưa ra nhận xét?

Bước 5: Thay đổi tần số xung đồng hồ f =10 Hz trên bộ phát tín hiệu. Quan sát tín hiệu ra và đưa ra nhận xét so với trường hợp ở bước 4.

Bước 6: Thay đổi biên độ tín hiệu xung đồng hồ A = 7V trên bộ phát tín hiệu. Quan sát các IC và giải thích hiện tượng?

Bước 7: Thay đổi điện áp nguồn cung cấp V = 10V, Quan sát các linh kiện trên mạch lắp ráp và giải thích hiện tượng?

Bước 8: Tiến hành lựa chọn sơ đồ nguyên lý bộ đếm thập phân (đếm ngược) và thực hành lắp ráp trên Test Board.

Người học truy cập Vào đây để xây dựng và test mạch nguyên lý.

Người học truy cấp Vào đây để thực hiện lắp ráp mạch trên Test Board.

Bước 2: Thay đổi tốc độ mô phỏng mạch và hiệu ứng tín hiệu của mạch bằng cách Click chuột vào các biểu tượng "Simulation Speed" và "Current Speed" tương ứng. Quan sát hiệu ứng trong mạch.

Bước 3: Thay đổi tần số của xung đồng hồ bằng cách Click đúp chuột vào biểu tượng "CLK". Quan sát tín hiệu ở đầu ra và giản đồ dạng sóng, So sánh với kết quả quan sát được ở bước thứ 1.

Bước 4: Tiến hành thực hành trên Test Board, Khởi chạy mạch lắp ráp. Quan sát tín hiệu ra, đưa ra nhận xét?

Bước 5: Thay đổi tần số xung đồng hồ f =10 Hz trên bộ phát tín hiệu. Quan sát tín hiệu ra và đưa ra nhận xét so với trường hợp ở bước 4.

Bước 6: Thay đổi biên độ tín hiệu xung đồng hồ A = 7V trên bộ phát tín hiệu. Quan sát các IC và giải thích hiện tượng?

Bước 7: Thay đổi điện áp nguồn cung cấp V = 10V, Quan sát các linh kiện trên mạch lắp ráp và giải thích hiện tượng?

Bước 8: Tiến hành lựa chọn sơ đồ nguyên lý bộ đếm thập phân (đếm ngược) và thực hành lắp ráp trên Test Board.

Người học truy cập Vào đây để xây dựng và test mạch nguyên lý.

Người học truy cấp Vào đây để thực hiện lắp ráp mạch trên Test Board.

:

I. SƠ ĐỒ MẠCH LOGIC

Click VÀO ĐÂY để thực hành

Click VÀO ĐÂY để thực hành

II. THỰC HÀNH TRÊN TEST BOARD