JK Flip-Flop bổ sung thêm trạng thái cho RS Flip-Flop (tránh trạng thái cấm), sơ đồ khối của JK Flip-Flop:

.png)

.png)

.png)

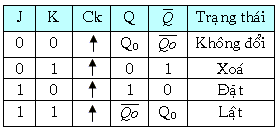

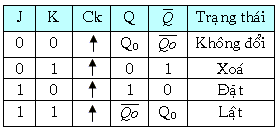

Bảng trạng thái của JK Flip-Flop như sau

Nhận thấy đầu vào J, K điều khiển trạng thái ngõ ra theo đúng như cách mà S R đã làm trừ 1 điểm là khi J = K = 1 thì trạng thái cấm được chuyển thành trạng thái ngược lại (với J = K = 0). Nó còn gọi là chế độ lật của hoạt động.

Từ dạng sóng có thể thấy rằng ngõ ra FF không bị ảnh hưởng bởi sườn xuống của xung ck các đầu vào J K cũng không có tác động trừ khi xảy ra tác động lên của Ck.

Sơ đồ logic JK–FFdùng cổng NAND:

Từ dạng sóng có thể thấy rằng ngõ ra FF không bị ảnh hưởng bởi sườn xuống của xung ck các đầu vào J K cũng không có tác động trừ khi xảy ra tác động lên của Ck.

Sơ đồ logic JK–FFdùng cổng NAND:

.png)

Bước 1: Khởi chạy mạch nguyên lý, thay đổi tổ hợp tín hiệu vào trên các đầu vào J, K và quan sát tín hiệu trên đầu ra đảo và không đảo?

Bước 2: Thay đổi tần số xung CLK = 100Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 3: Thay đổi tần số xung CLK = 5Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 4: giải thích mối quan hệ giữa tín hiệu CLK với thời gian chuyển trạng thái trên các đầu ra?

Bước 2: Thay đổi tần số xung CLK = 100Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 3: Thay đổi tần số xung CLK = 5Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 4: giải thích mối quan hệ giữa tín hiệu CLK với thời gian chuyển trạng thái trên các đầu ra?