Mạch dồn kênh hay còn gọi là mạch ghép kênh, đa hợp (Multiplexer-MUX) là 1 dạng mạch tổ hợp cho phép chọn 1 trong nhiều đường ngõ vào song song (các kênh vào) để đưa tới 1 ngõ ra (gọi là kênh truyền nối tiếp). Việc chọn đường nào trong các đường ngõ vào do các đầu vào điểu khiển quyết định. Ta thấy MUX hoạt động như 1 công tắc nhiều vị trí được điều khiển bởi mã số. Mã số này là dạng số nhị phân, tuỳ tổ hợp số nhị phân này mà ở bất kì thời điểm nào chỉ có 1 ngõ vào được chọn và cho phép đưa tới ngõ ra.

Mạch dồn kênh 2:1 có 2 đầu vào A, B ; 1 đầu ra Y và 1 đầu vào điều khiển S. Sơ đồ khối của mạch như sau:

.png)

.png)

Mạch dồn kênh 2:1 có 2 đầu vào A, B ; 1 đầu ra Y và 1 đầu vào điều khiển S. Sơ đồ khối của mạch như sau:

.png)

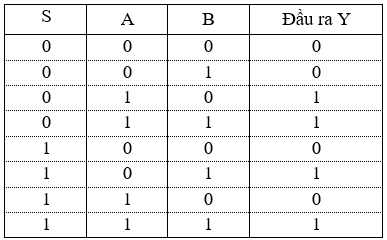

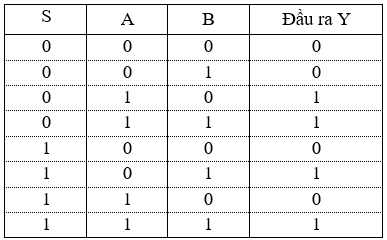

Bảng trạng thái của mạch dồn kênh 2:1

Ứng với trạng thái ngõ ra Y được quyết định bởi đầu vào điều khiển S. Khi S=0 dữ liệu A được đưa ra ngõ Y, khi S=1 dữ liệu B được đưa ra ngõ ra Y.

Sơ đồ mạch logic được xây dựng như sau:

Sơ đồ mạch logic được xây dựng như sau:

.png)

Bước 1: Khởi chạy mạch nguyên lý, thay đổi tổ hợp bit trên đầu vào điều khiển S và quan sát tín hiệu trên đầu ra? Đưa ra nhận xét?

Bước 2: Thay đổi dữ liệu trên các đầu vào A, B tương ứng với mỗi tổ hợp bit trên 2 đầu vào điều khiển, quan sát tín hiệu trên đầu ra? Đưa ra nhận xét?Bước 3: Khởi chạy mạch lắp ráp trên Testboard ảo, Bật tắt các công tắc tương ứng với các tín hiệu vào và tín hiệu điều khiển, quan sát độ sáng của LED và đưa ra nhận xét?

I. SƠ ĐỒ MẠCH LOGIC

Click VÀO ĐÂY để bắt đầu thực hành

II. THỰC HÀNH TRÊN TEST BOARD

Click VÀO ĐÂY để bắt đầu thực hành

II. THỰC HÀNH TRÊN TEST BOARD