Mạch phân kênh hoạt động ngược lại với mạch dồn kênh, nghĩa là đưa dữ liệu từ một đầu vào tới nhiều đầu ra song song, do đó nó còn có các tên như mạch tách kênh, giải đa hợp (DEMUX)... Mạch có một đầu vào dữ liệu, một đầu vào chọn mạch, n đầu vào điều khiển và 2n đầu ra.

Sơ đồ khối của mạch phân kênh 1:4 như hình dưới đây:

.png)

.png)

.png)

Sơ đồ khối của mạch phân kênh 1:4 như hình dưới đây:

.png)

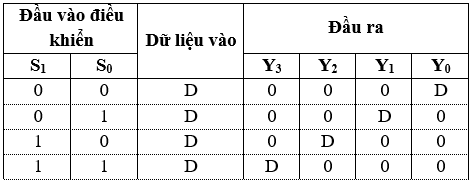

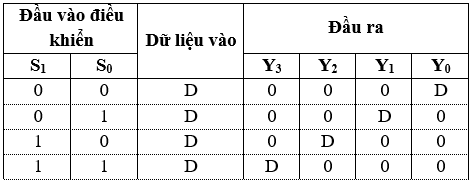

Mạch phân kênh 1:4 có 1 đầu vào dữ liệu D, 2 đầu vào điều khiển S0, S1 và 4 đầu ra Y0, Y1, Y2, Y3. Dữ liệu vào D được đưa ra ở đầu ra nào phụ thuộc vào tổ hợp bit của 2 đầu vào điều khiển. Ví dụ, khi tổ hợp bit đầu vào điều khiển (S0, S1) = (0,0) thì dữ liệu D sẽ được đưa ra ở đầu ra Y0, các đầu ra còn lại không có tín hiệu. Bảng trạng thái của mạch như sau:

Từ bảng trạng thái xây dựng được biểu thức các phương trình đầu ra:

.png)

Sơ đồ mạch logic được xây dựng từ phương trình hàm ra và bảng trạng thái như sau:

.png)

Bước 1: Khởi chạy mạch nguyên lý, thay đổi tổ hợp bit trên 3 đầu vào S0, S1 và quan sát tín hiệu trên các đầu ra?

Bước 2: Thay đổi dữ liệu trên đầu vào D, lặp lại bước 2 và đưa ra nhận xét?

Bước 3: Từ kết quả khảo sát, phân tích nguyên lý làm việc chung của mạch?

Bước 2: Thay đổi dữ liệu trên đầu vào D, lặp lại bước 2 và đưa ra nhận xét?

Bước 3: Từ kết quả khảo sát, phân tích nguyên lý làm việc chung của mạch?

I. SƠ ĐỒ MẠCH LOGIC

Click VÀO ĐÂY để bắt đầu thực hành

II. THỰC HÀNH TRÊN TEST BOARD

Click VÀO ĐÂY để bắt đầu thực hành

II. THỰC HÀNH TRÊN TEST BOARD