Một RS–FF đơn giản chỉ có hai đầu vào dữ liệu R (Reset) và S (Set), mà không có đầu vào xung nhịp và các đầu vào điều khiển không đồng bộ. Các đầu vào này được đặt tên theo chức năng: Set để đặt mức đầu ra Q = 1, Reset để xóa mức đầu ra Q = 0.

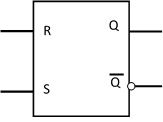

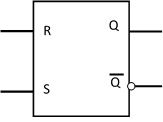

Sơ đồ khối của RS–FF không đồng bộ như hình dưới đây:

.png)

Sơ đồ khối của RS–FF không đồng bộ như hình dưới đây:

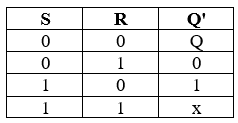

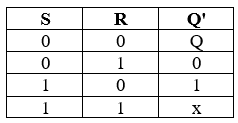

Bảng chân lý của RS–FF được cho ở dưới. Trong bảng này khi đầu vào Set có mức 1 thì đầu ra Q sẽ lên 1 dù giá trị trước đó là 0 hay 1 tùy ý. Tương tự đầu ra Q sẽ có mức 0 khi Reset có mức 1. Khi cả hai đầu vào Set và Reset có mức logic 0 thì đầu ra Q không thay đổi giá trị.

Sơ đồ logic FF-RSdùng cổng NAND như sau:

.png)

Bước 1: Khởi chạy mạch nguyên lý, thay đổi tổ hợp tín hiệu vào trên các đầu vào J, K và quan sát tín hiệu trên đầu ra đảo và không đảo?

Bước 2: Thay đổi tần số xung CLK = 100Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 3: Thay đổi tần số xung CLK = 5Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 4: giải thích mối quan hệ giữa tín hiệu CLK với thời gian chuyển trạng thái trên các đầu ra?

Bước 2: Thay đổi tần số xung CLK = 100Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 3: Thay đổi tần số xung CLK = 5Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 4: giải thích mối quan hệ giữa tín hiệu CLK với thời gian chuyển trạng thái trên các đầu ra?