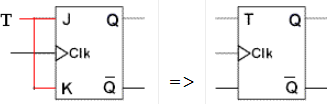

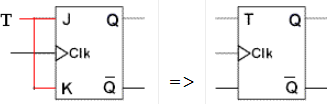

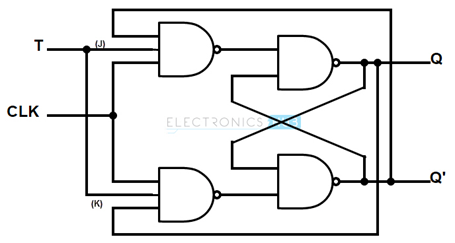

Khi nối chung 2 ngõ vào JK thì sẽ được T FLIP-FLOP chỉ có một ngõ vào T, ngõ ra sẽ bị lật lại trạng thái ban đầu khi ngõ T tác động và mỗi khi có cạnh sườn lên hay xuống của xung ck.

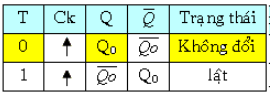

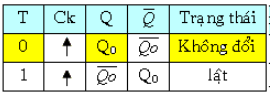

Sơ đồ khối và bảng trạng thái của FF T như sau:

Sơ đồ khối và bảng trạng thái của FF T như sau:

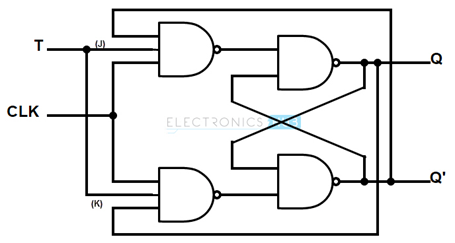

Sơ đồ mạch logic T FLIP-FLOP dùng cổng NAND:

T FLIP-FLOP được sử dụng chính để tạo mạch đếm chia 2. Khi T nối lên mức 1 (Vcc) hay để trống, xung kích lần lượt đưa vào ngõ Ck. Ngõ ra Q sẽ lật trạng thái mỗi lần ck xuống hay lên. Tần số xung ngõ ra Q chỉ còn bằng một nửa tần số ngõ vào ck nếu đưa Q này tới các tầng FF sau nữa thì lần lượt tần số f sẽ lại được chia đôi. Đây là nguyên lí chính của mạch đếm.

Bước 1: Khởi chạy mạch nguyên lý, thay đổi tín hiệu vào T và quan sát tín hiệu trên đầu ra đảo và không đảo?

Bước 2: Thay đổi tần số xung CLK = 100Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 3: Thay đổi tần số xung CLK = 5Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 2: Thay đổi tần số xung CLK = 100Hz, lặp lại bước 1 và đưa ra nhận xét?

Bước 3: Thay đổi tần số xung CLK = 5Hz, lặp lại bước 1 và đưa ra nhận xét?

II. THỰC HÀNH TRÊN TEST BOARD